# Introduction to FPGAs

IAS0600 Digital Systems Design with VHDL

Jaan Raik, Natalia Cherezova

#### Introduction to FPGAs

- History of FPGAs

- Reconfigurable hardware vs integrated circuits

- FPGA applications

- Inner architecture of FPGAs

- Design flow for FPGA

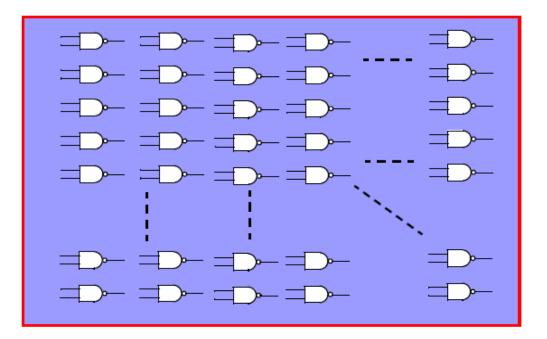

#### History. Gate Arrays

- In the beginning, digital design was done with the '74 series of chips.

- Some people would design their own chips based on Gate Arrays, which were nothing else than an array of NAND gates:

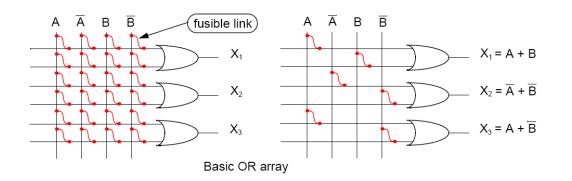

## History. PLA/PLD

- The first programmable chips were PLAs (Programmable Logic Arrays): two level structures of AND and OR gates with user programmable connections.

- Programmable Array Logic devices were an improvement in structure and cost over PLAs. Today such devices are generically called Programmable Logic Devices (PLDs).

## History. CPLD/FPGA

- A complex PLD (CPLD) is nothing else than a collection of multiple PLDs and an interconnection structure.

- Compared to a CPLD, a Field Programmable Gate Array (FPGA) contains a much larger number of smaller individual blocks + large interconnection structure that dominates the entire chip.

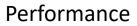

### Reconfigurable hardware vs ICs

- Traditional IC

- Once fabricated cannot be changed

- Examples: CPU, GPU, TPU

- Reconfigurable hardware

- Does not implement a specific circuit functionality

- Can be reconfigured to implement any desired functionality/circuit

- Can be reconfigured many times during the lifetime

- Offer a flexible platform for increasingly complex systems

- Example: FPGA (Field-Programmable Gate Array)

### Reconfigurable hardware vs ICs

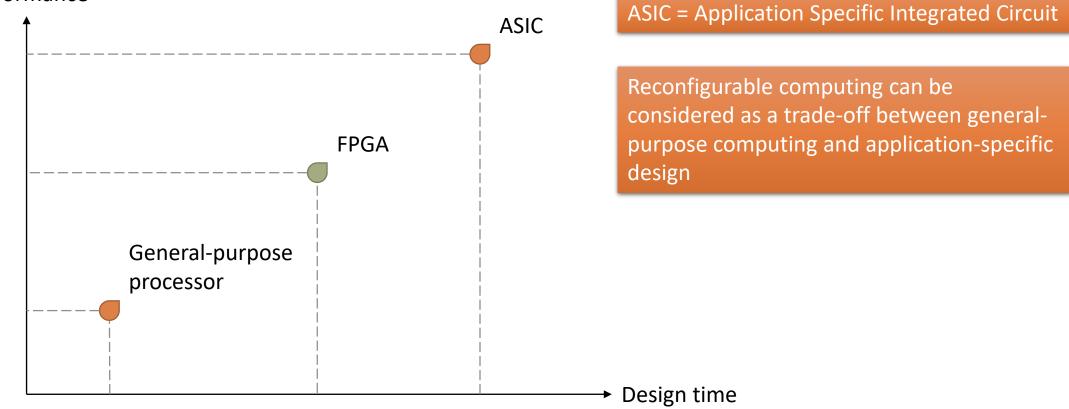

#### Reconfigurable hardware vs ICs

• FPGAs are less costly with smaller volumes due to lower Non-Recurring Engineering (NRE) costs:

#### **FPGA** applications

Aerospace (satellites, planes)

Military equipment

Medical devices

Automotive industry

High-end broadcast systems

Wired and wireless communication

Production line robots

Video processing and surveillance

Data centers

AI/ML applications

## **Examples of FPGA applications**

#### • NASA

- Mars Science Lab mission (Curiosity)

- Mars Exploration Rover mission (Spirit, Opportunity)

- Mars 2020 Perseverance rover

- Microsoft

- Bing indexing acceleration

- Deep learning acceleration in Azure cloud

- Amazon

- Amazon Elastic Compute Cloud (EC2) F1 instances

aws

https://www.xilinx.com/about/blogs/xilinx-xclusive-blog/2021/rover-lands-on-mars-with-xilinx-fpgas-on-board.html

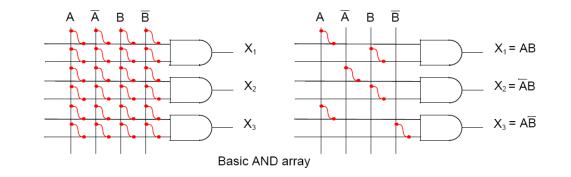

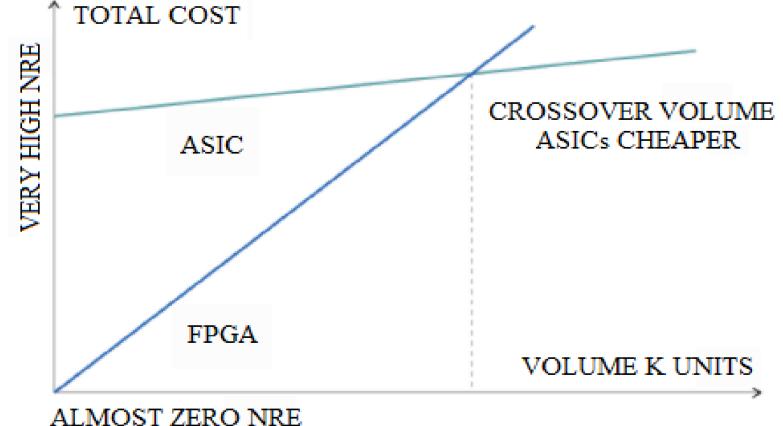

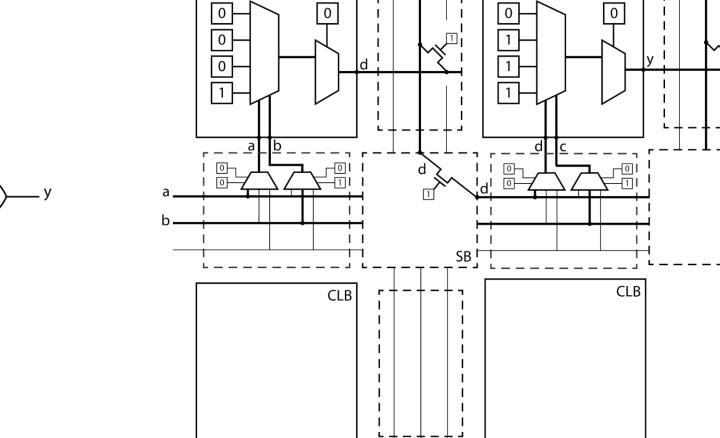

- Basic blocks:

- Configurable Logic Block (CLB)

- Implement logic functions

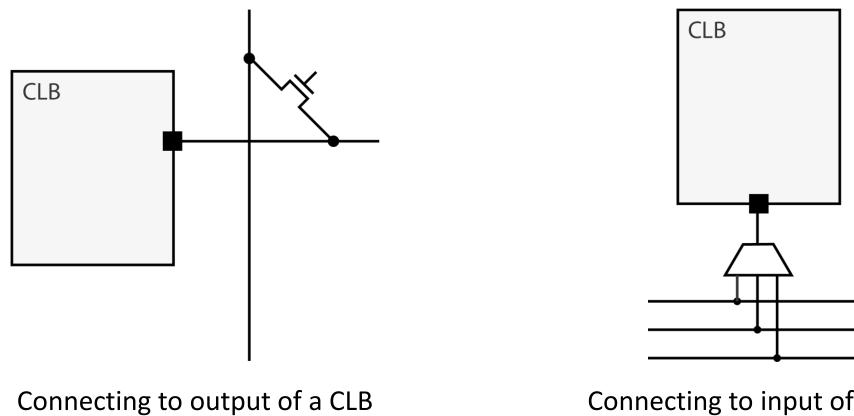

- Connection Box (CB)

- Connect inputs and outputs of CLBs to the connection wires

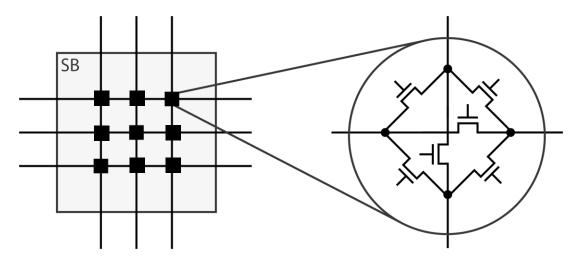

- Switch Box (SB)

- Connect vertical and horizontal wires

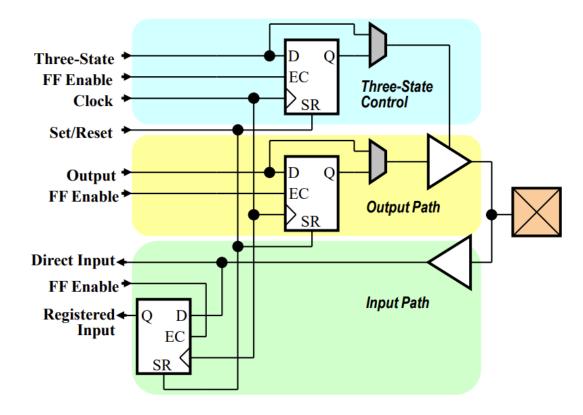

- Input/Output Block (IOB)

- Connect IO pins with the internal resources

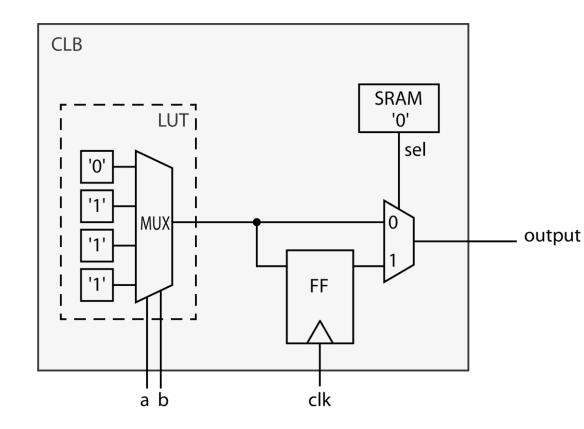

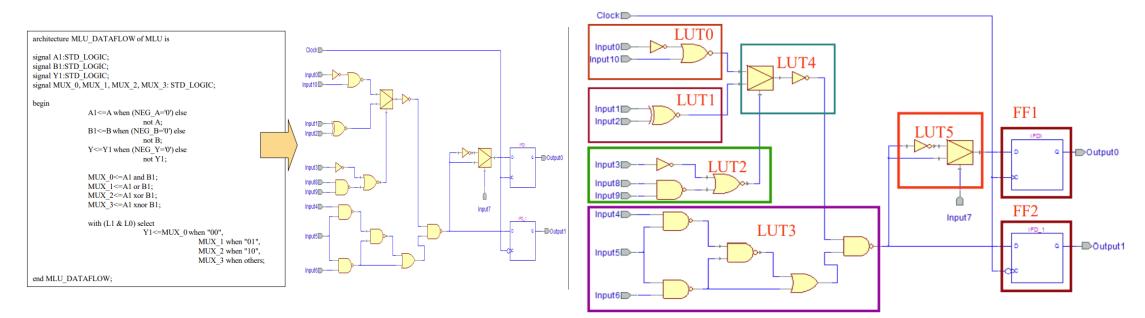

## Configurable Logic Block

- Look-up Table (LUT) implements a combinational logic function

- Stores a truth table of the function

- Inputs act as an address or index of the table cell

- Register (flip-flop FF) optionally stores the output of LUT

- MUX selects the output of the CLB

#### Switch Box

- Each switch point consists of six programmable switches

- Switches are controlled by configuration memory cells

#### **Connection Box**

Connecting to input of a CLB

## Input/Output Block

Cristinel Ababei, EECE-4740 Advanced VHDL and FPGA Design [lecture slides]

- Each IOB can work as a uni- or bidirectional IO

- Outputs can be forced into highimpedance

- Inputs and outputs can be latched to registers

### Example

d

a

b

С

CLB

0

v

0

## FPGA technology

- Antifuse

- One-time programmable

- Flash

- Non-volatile memory  $\rightarrow$  configuration is not lost when the power is down

- Limited re-programmability

- SRAM

- Volatile memory

- Easily re-programmable

### **FPGA vendors**

• AMD-Xilinx Inc. ]

~90% of the market

- Intel (Altera)

- Microchip

- Lattice Semiconductor

- QuickLogic Corporation

- Achronix

- Efinix Inc.

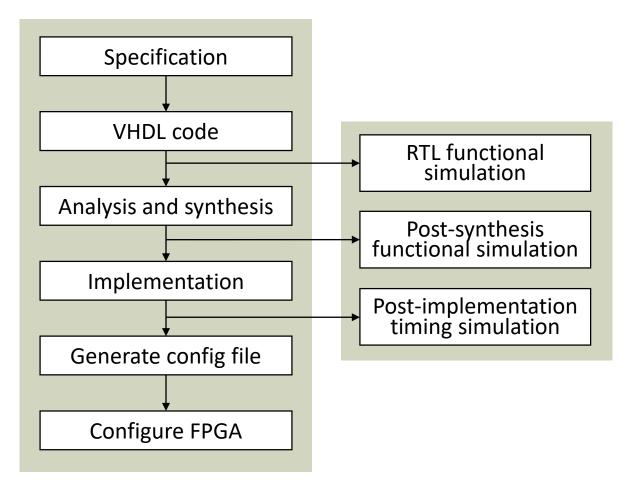

## Design flow for FPGA

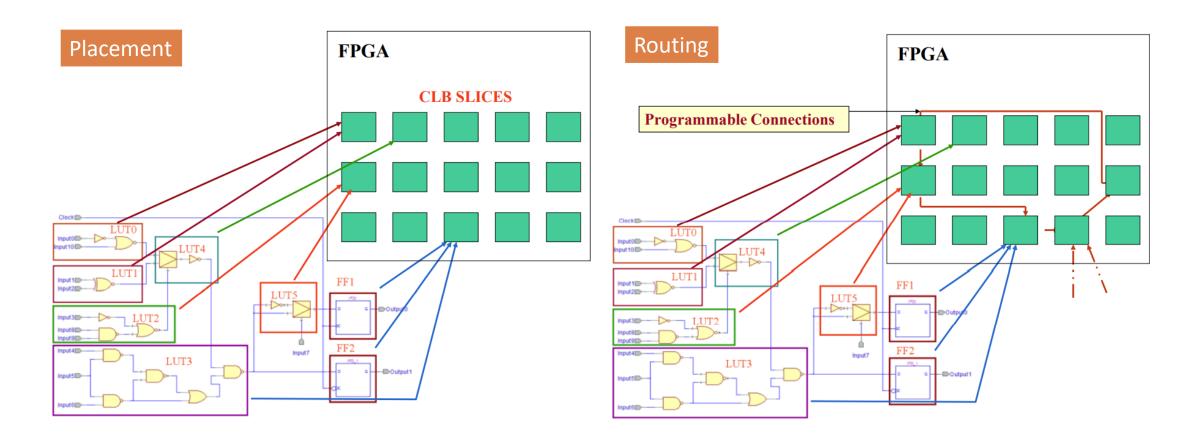

- Synthesis is the transformation of the HDL description into HW components

- Implementation combines placement and routing

- Configuration file (bitstream) is loaded into configuration memory

## Synthesis

#### HDL description $\rightarrow$ HW components

#### Technology mapping

Cristinel Ababei, EECE-4740 Advanced VHDL and FPGA Design [lecture slides]

### Implementation

Cristinel Ababei, EECE-4740 Advanced VHDL and FPGA Design [lecture slides]

## Configuration

- Once a design is implemented, you must create a file that the FPGA can understand

- This file is called a bitstream: a BIT file

- Bitstream holds values that will be loaded into configuration memory

- LUT values

- Routing configuration

- Control signals for CLBs and IOBs